# **Document Title**

### 2Mx16 bit Uni-Transistor Random Access Memory

## **Revision History**

| Revision No. | History                                                                                 | Draft Date       | <u>Remark</u> |

|--------------|-----------------------------------------------------------------------------------------|------------------|---------------|

| 0.0          | Initial Draft                                                                           | January 16, 2003 | Advanced      |

| 0.1          | Revised<br>- Deleted 60ns Speed Bin                                                     | June 13, 2003    | Preliminary   |

| 0.2          | Revised<br>- Corrected errorta '48-TBGA' under PIN DESCRIPTION to '48-FBGA'<br>on page2 | August 13, 2003  | Preliminary   |

The attached datasheets are provided by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications and products. SAMSUNG Electronics will answer to your questions about device. If you have any questions, please contact the SAMSUNG branch offices.

# 2M x 16 bit Uni-Transistor CMOS RAM

#### **FEATURES**

- Process Technology: CMOS

- Organization: 2M x16 bit

- Power Supply Voltage: 2.7V~3.1V

- Three State Outputs

- Compatible with Low Power SRAM

- Dual Chip selection support

- Package Type: 48-FBGA-6.00x8.00

### PRODUCT FAMILY

#### **GENERAL DESCRIPTION**

The K1S321611C is fabricated by SAMSUNG's advanced CMOS technology using one transistor memory cell. The device supports Industrial temperature range and 48 ball Chip Scale Package for user flexibility of system design. The device also supports dual chip selection for user interface.

|                |                      |           |       | Power Di                | ssipation                 |                   |

|----------------|----------------------|-----------|-------|-------------------------|---------------------------|-------------------|

| Product Family | Operating Temp.      | Vcc Range | Speed | Standby<br>(Isв1, Max.) | Operating<br>(Icc2, Max.) | РКС Туре          |

| K1S321611C-I   | Industrial(-40~85°C) | 2.7V~3.1V | 70ns  | 100µA                   | 35mA                      | 48-FBGA-6.00x8.00 |

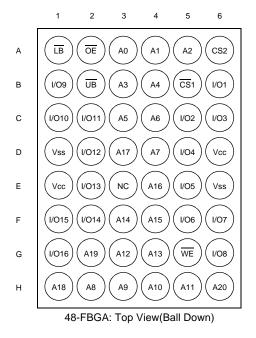

### **PIN DESCRIPTION**

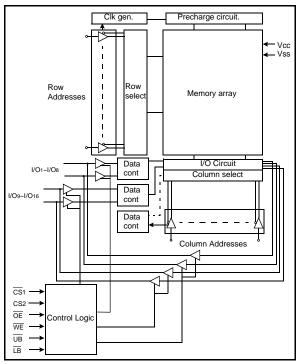

| FUNCTIONAL BLOCK DIAGRAM |

|--------------------------|

|--------------------------|

| Name       | Function            | Name | Function                    |

|------------|---------------------|------|-----------------------------|

| CS1,CS2    | Chip Select Inputs  | Vcc  | Power                       |

| OE         | Output Enable Input | Vss  | Ground                      |

| WE         | Write Enable Input  | UB   | Upper Byte(I/O9~16)         |

| A0~A20     | Address Inputs      | LB   | Lower Byte(I/O1~8)          |

| I/O1~I/O16 | Data Inputs/Outputs | NC   | No Connection <sup>1)</sup> |

1) Reserved for future use.

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

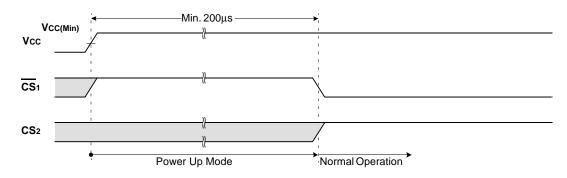

### POWER UP SEQUENCE

1. Apply power.

2. Maintain stable power(Vcc min.=2.7V) for a minimum 200 $\mu$ s with  $\overline{CS1}$ =high.or CS2=low.

TIMING WAVEFORM OF POWER UP(1) (CS1 controlled)

POWER UP(1)

1. After Vcc reaches Vcc(Min.), wait 200 $\mu$ s with  $\overline{CS}$ 1 high. Then the device gets into the normal operation.

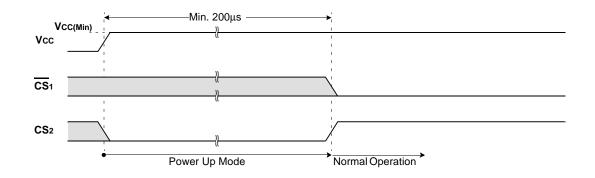

#### TIMING WAVEFORM OF POWER UP(2) (CS2 controlled)

POWER UP(2)

1. After Vcc reaches Vcc(Min.), wait 200 $\mu$ s with CS2 low. Then the device gets into the normal operation.

### FUNCTIONAL DESCRIPTION

| CS1             | CS2             | OE              | WE              | LB              | UB              | <b>I/O</b> 1~8 | <b>I/O</b> 9~16 | Mode             | Power   |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|------------------|---------|

| Н               | X <sup>1)</sup> | High-Z         | High-Z          | Deselected       | Standby |

| X <sup>1)</sup> | L               | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | Deselected       | Standby |

| X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | н               | н               | High-Z         | High-Z          | Deselected       | Standby |

| L               | Н               | Н               | Н               | L               | X <sup>1)</sup> | High-Z         | High-Z          | Output Disabled  | Active  |

| L               | Н               | Н               | Н               | X <sup>1)</sup> | L               | High-Z         | High-Z          | Output Disabled  | Active  |

| L               | Н               | L               | Н               | L               | Н               | Dout           | High-Z          | Lower Byte Read  | Active  |

| L               | Н               | L               | Н               | Н               | L               | High-Z         | Dout            | Upper Byte Read  | Active  |

| L               | Н               | L               | Н               | L               | L               | Dout           | Dout            | Word Read        | Active  |

| L               | Н               | X <sup>1)</sup> | L               | L               | Н               | Din            | High-Z          | Lower Byte Write | Active  |

| L               | Н               | X <sup>1)</sup> | L               | Н               | L               | High-Z         | Din             | Upper Byte Write | Active  |

| L               | Н               | X <sup>1)</sup> | L               | L               | L               | Din            | Din             | Word Write       | Active  |

1. X means don't care.(Must be low or high state)

### ABSOLUTE MAXIMUM RATINGS<sup>1)</sup>

| Item                                  | Symbol    | Ratings          | Unit |

|---------------------------------------|-----------|------------------|------|

| Voltage on any pin relative to Vss    | Vin, Vout | -0.2 to Vcc+0.3V | V    |

| Voltage on Vcc supply relative to Vss | Vcc       | -0.2 to 3.6V     | V    |

| Power Dissipation                     | PD        | 1.0              | W    |

| Storage temperature                   | Тѕтс      | -65 to 150       | °C   |

| Operating Temperature                 | Та        | -40 to 85        | °C   |

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to be used under recommended operating condition. Exposure to absolute maximum rating conditions longer than 1 second may affect reliability.

### **PRODUCT LIST**

| Industrial Temperature Products(-40~85°C) |                     |  |  |  |

|-------------------------------------------|---------------------|--|--|--|

| Part Name Function                        |                     |  |  |  |

| K1S321611C-FI70                           | 48-FBGA, 70ns, 2.9V |  |  |  |

### **RECOMMENDED DC OPERATING CONDITIONS<sup>1)</sup>**

| Item               | Symbol | Min                | Тур | Max       | Unit |

|--------------------|--------|--------------------|-----|-----------|------|

| Supply voltage     | Vcc    | 2.7                | 2.9 | 3.1       | V    |

| Ground             | Vss    | 0                  | 0   | 0         | V    |

| Input high voltage | Viн    | 2.2                | -   | Vcc+0.32) | V    |

| Input low voltage  | VIL    | -0.3 <sup>3)</sup> | -   | 0.6       | V    |

1. TA=-40 to  $85^{\circ}C$ , otherwise specified.

Overshoot: Vcc+1.0V in case of pulse width ≤20ns.

Undershoot: -1.0V in case of pulse width ≤20ns.

Overshoot and undershoot are sampled, not 100% tested.

### CAPACITANCE<sup>1)</sup>(f=1MHz, TA=25°C)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input capacitance        | CIN    | VIN=0V         | -   | 8   | pF   |

| Input/Output capacitance | Сю     | Vio=0V         | -   | 10  | pF   |

1. Capacitance is sampled, not 100% tested.

## DC AND OPERATING CHARACTERISTICS

| Item                      | Symbol | Test Conditions                                                                                                                                                       | Min | Тур | Max | Unit |

|---------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input leakage current     | L      | VIN=Vss to Vcc                                                                                                                                                        | -1  | -   | 1   | μA   |

| Output leakage current    | Ilo    | $\overline{CS}$ 1=VIH or CS2=VIL or $\overline{OE}$ =VIH or $\overline{WE}$ =VIL or $\overline{LB}$ = $\overline{UB}$ =VIH, VIO=VSS to Vcc                            | -1  | -   | 1   | μΑ   |

| Average operating current | ICC1   | Cycle time=1µs, 100% duty, lio=0mA, CS1≤0.2V, LB≤0.2V<br>or/and UB≤0.2V, CS2≥Vcc-0.2V, ViN≤0.2V or ViN≥Vcc-0.2V                                                       | -   | -   | 7   | mA   |

|                           | ICC2   | Cycle time=Min, Iю=0mA, 100% duty, CS1=ViL, CS2=Viн<br>LB=ViL or/and UB=ViL, ViN=Viн or ViL                                                                           | -   | -   | 35  | mA   |

| Output low voltage        | Vol    | IOL = 2.1mA                                                                                                                                                           | -   | -   | 0.4 | V    |

| Output high voltage       | Vон    | Iон = -1.0mA                                                                                                                                                          | 2.4 | -   | -   | V    |

| Standby Current(CMOS)     | ISB1   | Other inputs=0~Vcc<br>1) $\overline{CS}1 \ge Vcc-0.2V$ , $CS2 \ge Vcc-0.2V(\overline{CS}1 \text{ controlled})$ or<br>2) $0V \le CS2 \le 0.2V(CS2 \text{ controlled})$ | -   | -   | 100 | μΑ   |

### AC OPERATING CONDITIONS

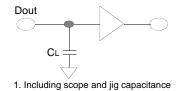

**TEST CONDITIONS**(Test Load and Test Input/Output Reference) Input pulse level: 0.4 to 2.2V Input rising and falling time: 5ns Input and output reference voltage: 1.5V Output load (See right): CL=50pF

#### AC CHARACTERISTICS(Vcc=2.7~3.1V, TA=-40 to 85°C)

|       |                                 |        | Spe              | ed                         |       |  |

|-------|---------------------------------|--------|------------------|----------------------------|-------|--|

|       | Parameter List                  | Symbol | 70               | ns                         | Units |  |

|       |                                 |        | Min              | Min     Max       70     - |       |  |

|       | Read Cycle Time                 | tRC    | 70               | -                          | ns    |  |

|       | Address Access Time             | tAA    | -                | 70                         | ns    |  |

|       | Chip Select to Output           | tco    | -                | 70                         | ns    |  |

|       | Output Enable to Valid Output   | tOE    | -                | 35                         | ns    |  |

|       | UB, LB Access Time              | tBA    | -                | 70                         | ns    |  |

| Read  | Chip Select to Low-Z Output     | tLZ    | 10               | -                          | ns    |  |

| Reau  | UB, LB Enable to Low-Z Output   | tBLZ   | 10               | -                          | ns    |  |

|       | Output Enable to Low-Z Output   | toLz   | 5                | -                          | ns    |  |

|       | Chip Disable to High-Z Output   | tHZ    | 0                | 25                         | ns    |  |

|       | UB, LB Disable to High-Z Output | tвнz   | 0                | 25                         | ns    |  |

|       | Output Disable to High-Z Output | tонz   | 0                | 25                         | ns    |  |

|       | Output Hold from Address Change | toн    | 5                | -                          | ns    |  |

|       | Write Cycle Time                | twc    | 70               | -                          | ns    |  |

|       | Chip Select to End of Write     | tcw    | 60               | -                          | ns    |  |

|       | Address Set-up Time             | tas    | 0                | -                          | ns    |  |

|       | Address Valid to End of Write   | tAW    | 60               | -                          | ns    |  |

|       | UB, LB Valid to End of Write    | tBW    | 60               | -                          | ns    |  |

| Write | Write Pulse Width               | tWP    | 55 <sup>1)</sup> | -                          | ns    |  |

|       | Write Recovery Time             | twr    | 0                | -                          | ns    |  |

|       | Write to Output High-Z          | twnz   | 0                | 25                         | ns    |  |

|       | Data to Write Time Overlap      | tDW    | 30               | -                          | ns    |  |

|       | Data Hold from Write Time       | tdн    | 0                | -                          | ns    |  |

|       | End Write to Output Low-Z       | tow    | 5                | -                          | ns    |  |

1. tWP(min)=70ns for continuous write operation over 50 times.

#### TIMING DIAGRAMS

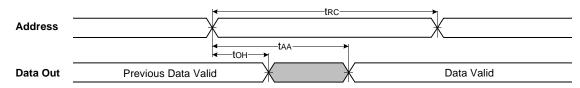

TIMING WAVEFORM OF READ CYCLE(1) (Address Controlled, CS1=OE=VIL, CS2=WE=VIH, UB or/and LB=VIL)

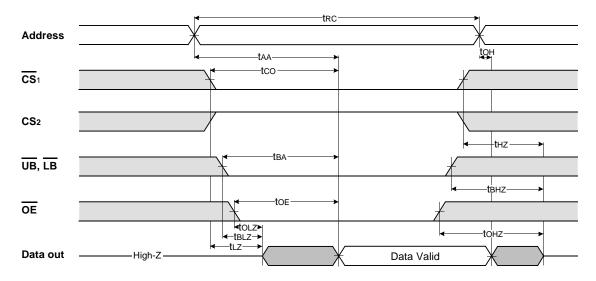

#### TIMING WAVEFORM OF READ CYCLE(2) (WE=VIH)

#### NOTES (READ CYCLE)

- 1. tHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- 2. At any given temperature and voltage condition, tHZ(Max.) is less than tLZ(Min.) both for a given device and from device to device interconnection.

- 3. tOE(max) is met only when  $\overline{OE}$  becomes enabled after tAA(max).

- 4. If invalid address signals shorter than min. tRC are continuously repeated for over 4us, the device needs a normal read timing(tRC) or needs to sustain standby state for min. tRC at least once in every 4us.

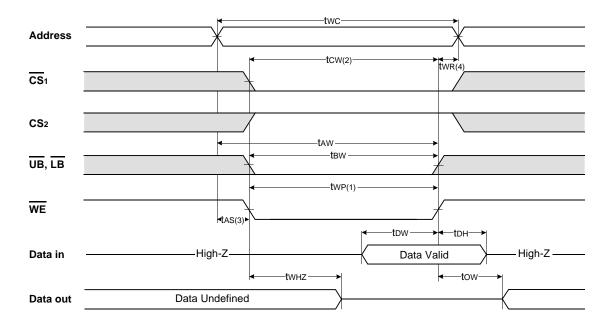

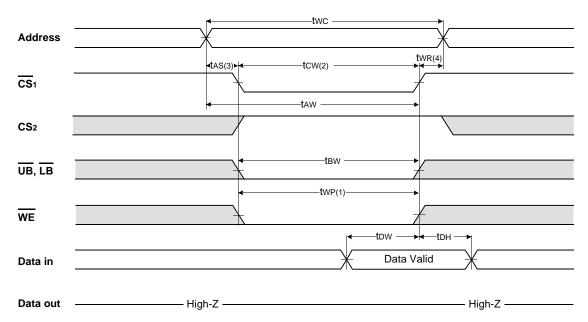

#### TIMING WAVEFORM OF WRITE CYCLE(1) (WE Controlled)

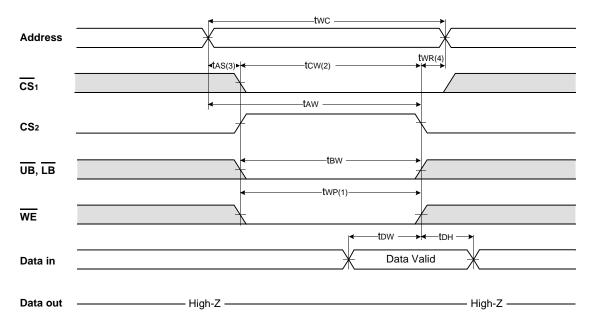

#### TIMING WAVEFORM OF WRITE CYCLE(2) (CS1 Controlled)

#### TIMING WAVEFORM OF WRITE CYCLE(3) (CS2 Controlled)

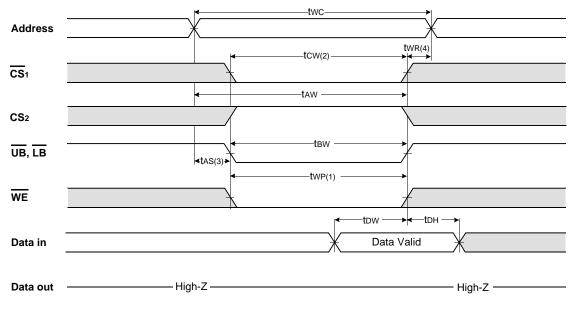

#### TIMING WAVEFORM OF WRITE CYCLE(4) (UB, LB Controlled)

#### NOTES (WRITE CYCLE)

1. <u>A write occurs during the overlap(twp) of low CS1 and low WE. A write begins when CS1 goes low and WE goes low with asserting UB or LB for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest tran-</u> sition when CS1 goes high and WE goes high. The twp is measured from the beginning of write to the end of write.

tcw is measured from the CS1 going low to the end of write.

tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with CS1 or WE going high.

Preliminary UtRAM

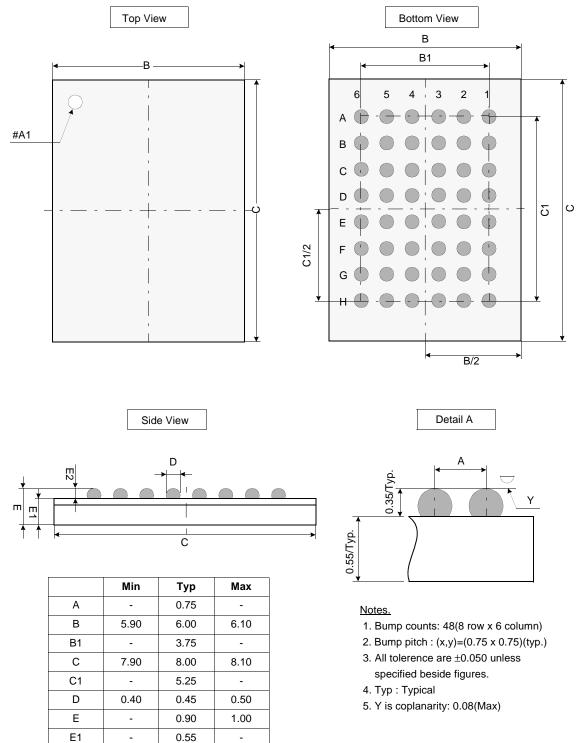

Unit: millimeters

### PACKAGE DIMENSION

48 BALL FINE PITCH BGA(0.75mm ball pitch)

E2

Υ

0.30

-

0.35

-

0.40

0.08